PVTバラつき補正技術

ある日,新しい金属が発見され,それを使えばとても切れ味の良い刃物が造れる一方,打ち方を誤ると今までより切れ味が悪くなってしまうことが分かりました.

その金属を使えば価値の高い刃物が造れますが,切れ味の良いものばかりを造るのは難しく,たくさん造って儲けるのは難しそうです.

一方,別の金属を混ぜれば製造しやすくはなりますが,その分切れ味が悪くなり,新しい金属の価値を活かせなくなってしまいます.

もし,打ち方を誤った刃物にかけることで,その潜在的な切れ味を引き出せるような魔法があったとしたら…?この研究はそんな考え方をLSI設計に取り入れようという研究です.

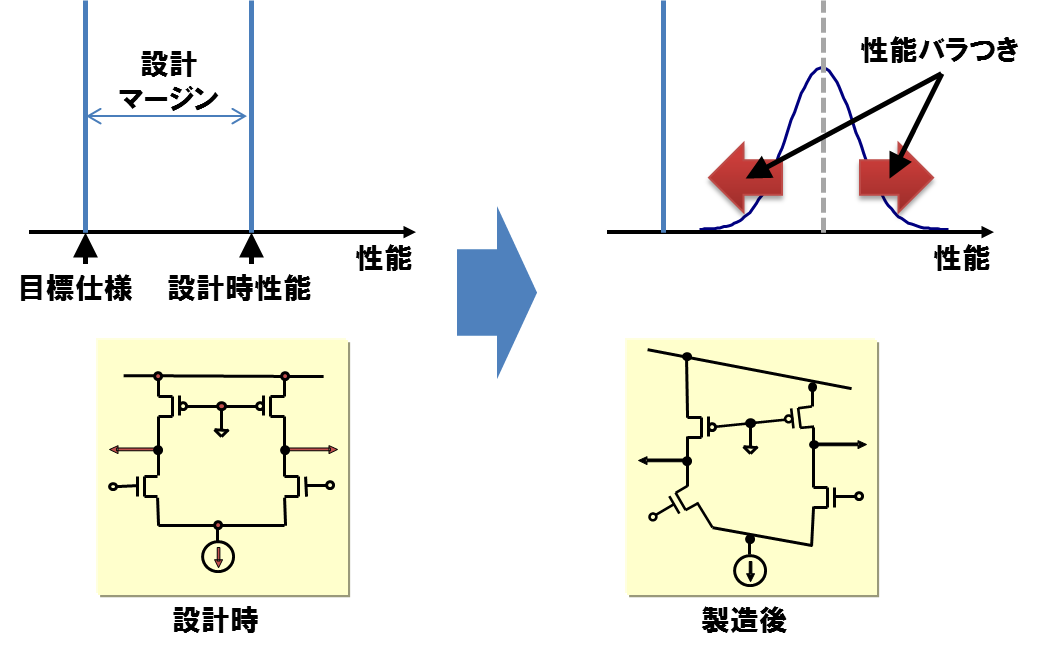

近年のVLSI設計においては,設計プロセス(半導体素子のサイズ,配線幅)の極限的微細化にともなって生じる製造プロセス(P),電源電圧(V),温度(T)のバラつきの増大が,VLSIの性能向上を妨げる大きな障害となっています.通常,回路設計においては,バラつきにともなう回路性能のゆらぎを考慮し,十分な動作マージンを取った上で設計が行われます.これは,回路の「性能」をある程度犠牲にしつつ,回路の「信頼性」を十分な高さまで引き上げる作業とも言えます.しかし,チップ上に集積されたたくさんの素子それぞれにおけるバラつきの影響を全て考慮して設計しようとした場合,確保しなければならないマージンが非常に大きくなってしまうため,回路性能(動作速度,回路面積など)の低下や,製造コストの増加に繋がります.微細化がさらに進行し,バラつきの影響がますます増加することが予測されている今,従来の設計法によって高信頼性と高性能性が両立したVLSIを実現することは極めて困難になりつつあります.

以上の問題を解決することを目的とし,近年,製造後の動作特性に応じて性能調整を行うような補正を実現する「ポストプロセスバラつき補正技術」の研究が広く行われています.これは,バラつきの影響をモニタリングし,LSI内部に組み込んだ補正用回路を制御することで,LSI製造時あるいは動作時に生じるバラつきの影響を補償する技術です. この技術を活用することで,単にバラつきを吸収し,与えられた設計仕様に対する安定動作を確保することのみに留まらず,①環境に応じたチューニングを施すことで,与えられた動作マージン内における最適な動作性能を維持できる,②より幅広い環境変化にも適応できる,といった点が期待できます.

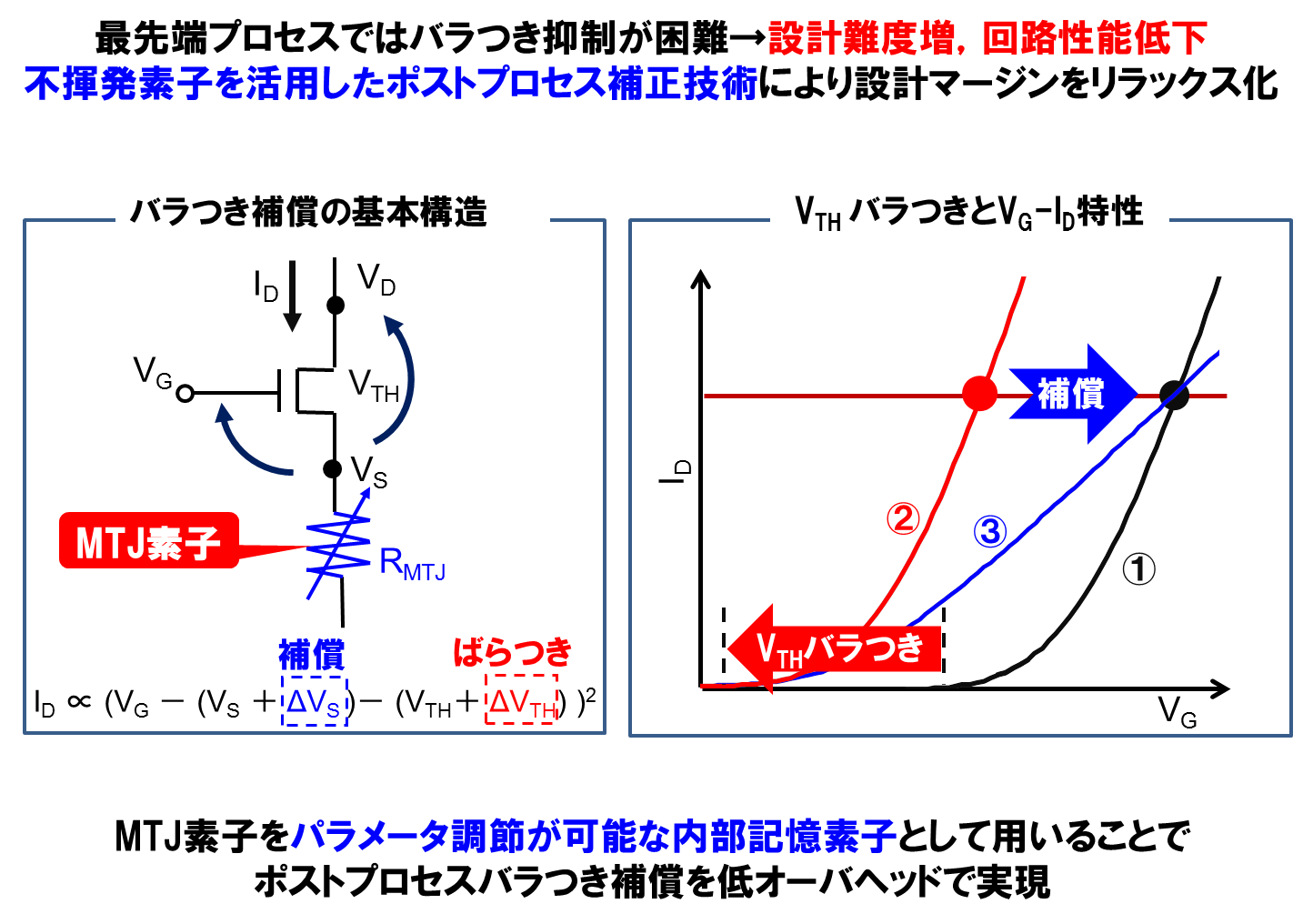

バラつき補正機能という高信頼性と,VLSIシステムにおける高性能性・低消費電力性を両立させるためには,回路自体が動作特性に関してプログラマブルな構造をしており,かつ,プログラムした動作点をできるだけ低コストのハードウェアで実現されなければなりません.しかし,一般的なばらつき補正方式においては,回路本来の機能とは関係の無い,特性制御用にのみ用いられる回路ブロックを回路内に組み込む必要があるため,回路面積に対するオーバーヘッドが生じるという問題がありました.

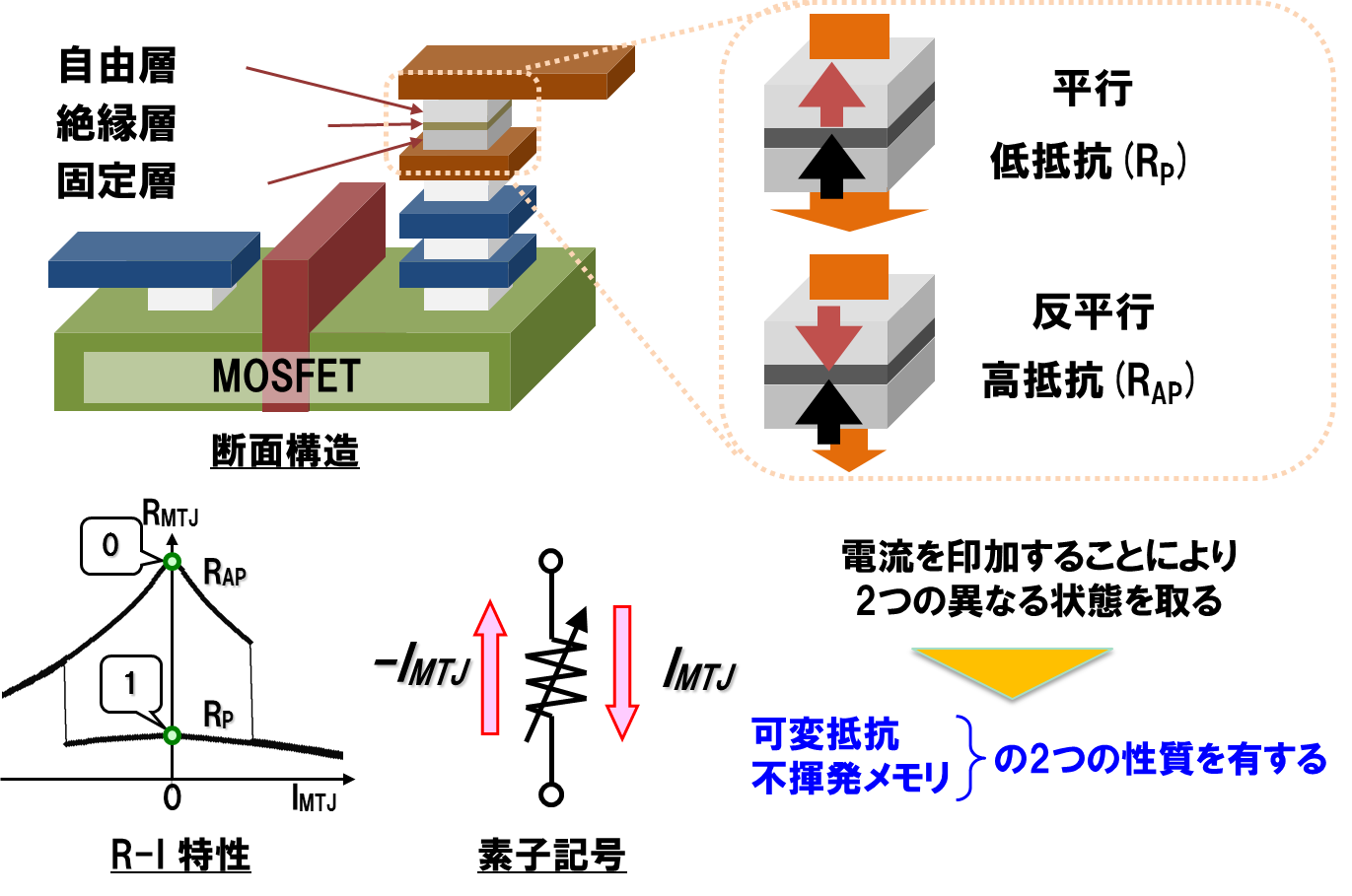

そこで,本研究室では,補正機能実現のためのハードウェアコストを十分小さく抑えられ,かつ高性能化・低消費電力化も同時に達成できる回路構成方式として,MTJ(Magnetic Tunnel Junction)素子[1][2]と呼ばれる不揮発性デバイスを用いたバラつき補正機能付き回路構造を提案し,バラつき補正機能という高信頼性と,VLSIシステムにおける高性能性・低消費電力性の両立を目指しています.

MTJ素子を用いた提案回路では,バラつき補正情報をMTJ素子に記憶します.このMTJ素子は,CMOS層の上部に積層できるため,ハードウェアコストが十分小さく,極めて小規模な基本回路ごとに補正機能が付加できます.

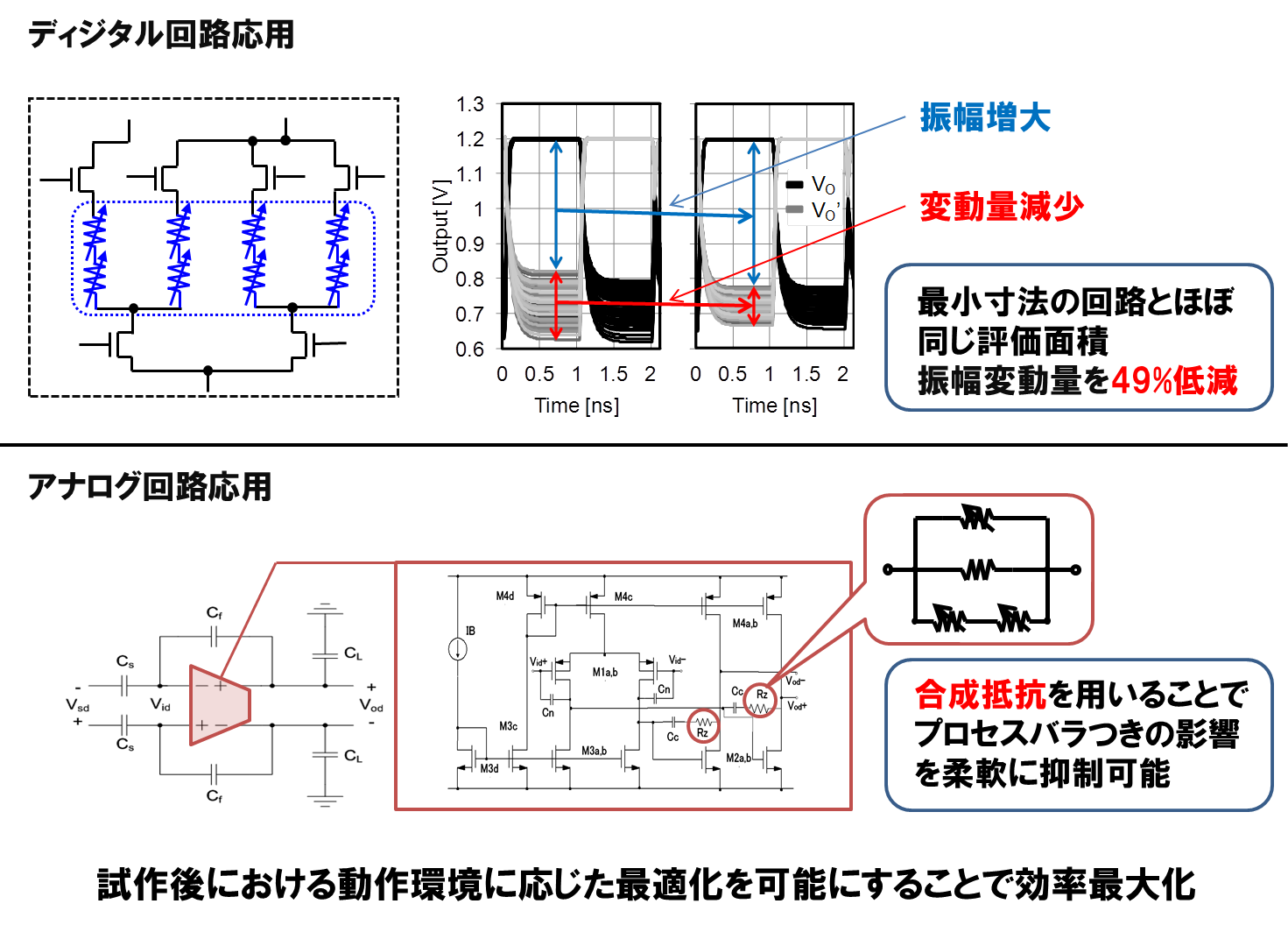

現在までに,ディジタル論理回路における振幅変動の補償[3]や,アナログ回路におけるプロセスバラつき補償[4][5]といった具体的応用例を通し,その有効性を実証してきています.

LSIに求められる性能がますます高度化・多様化していく将来,バラつきの影響を抑制しつつ,プロセス改善によって得られる性能向上の可能性を最大限活かすような設計技術の重要性はますます高まると予想されます.本研究では,新機能素子による「再構成可能LSI技術」に加え,環境に応じた最適動作点を探索するための「最適化アルゴリズム」,そしてそれらを統合したシステムのための「新概念LSI設計論」との組合せによる総合的なアプローチにより,従来の設計技術では実現し得ない「知的環境適応型LSI」の実現に向けた研究を進めています.

参考文献:

- S. Ikeda,et al., "Magnetic tunnel junctions for spintronic memories and beyond," IEEE Trans. Electron Devices vol.54, iss.5, pp.991–1002, 2007.

- S. Ikeda, et al., "A perpendicular-anisotropy CoFeB–MgO magnetic tunnel junction," Nature Materials vol.9, pp.721–724, 2010.

- Y. Kim, et al., "Variation-Resilient Current-Mode Logic Circuit Design Using MTJ Devices," 2012 IEEE International Symposium on Circuits & Systems (ISCAS2012), pp.2705-2708, May 2012.

- M. Natsui, et al., "Process-Variation-Resilient OTA Using MTJ-based Multi-level Resistance Control," 42nd IEEE International Symposium on Multiple-Valued Logic (ISMVL2012), pp.214-219, May 2012.

- M. Natsui, et al., "Design of Process-Variation-Resilient Analog Basic Components Using Magnetic-Tunnel-Junction Devices," Journal of Multiple-Valued Logic and Soft Computing, Vol.21, No.5-6, pp.597-608, 2013.