MTJベース不揮発FPGA

Contents

背景

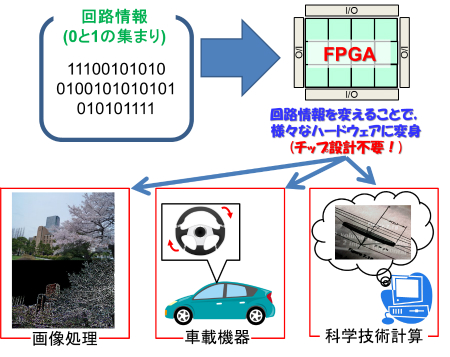

デジタル集積回路はスマートフォンやタブレット端末,家電製品,自動車など私たちの生活に必要不可欠な存在となっており,用途に応じて多種多様な機能が求められています。さらにこのような要求にこたえるため,デジタル集積回路には「安さ」,「早さ」,「柔軟さ」が求められています。FPGA (Field-Programmable Gate Array)は,このような多種多様性に対応できるハードウェアとして近年特に活用事例が増えております。従来,デジタル集積回路は目的に応じて個別にチップ設計が必要でした。これに対してFPGAでは,回路情報といわれる'0'と'1'の集まりを内部のメモリに書込むだけで,1つのチップを様々なハードウェアに変身させることができます。

例として,エッジ抽出などの画像処理用ハードウェアや,自動車の自動運転制御など車載機器への応用,またFPGAの構造を活用した大規模な科学技術演算処理などが挙げられます (図1)。

これまでFPGAは,トランジスタの微細加工技術の発展とともに高集積化,高性能化を続けてきました。しかし,微細加工技術のみに頼った進化に限界が見えつつあります。その最大の要因が何もしていない状態で消費される電力,すなわち待機電力です。待機電力はトランジスタが微細になればなるほど増大し,最先端の加工技術では動作時に消費する電力よりも大きいとまでされています。こういった背景から,FPGAの進化は徐々に頭打ちとなってしまっており,新たなブレークスルーが求められています。

不揮発FPGA

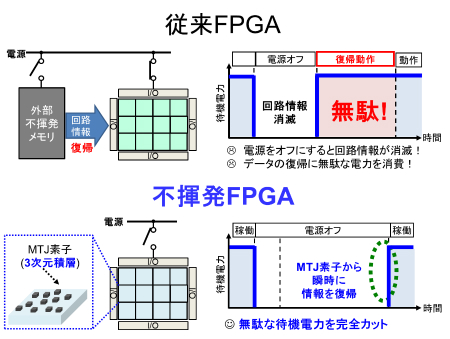

このような問題を解決するため,本研究室ではトンネル磁気接合素子 (MTJ: Magnetic Tunnel Junction)素子に回路情報記憶する不揮発FPGAに関する研究を行っております。従来のFPGAでは電気によって回路情報を保持しているため,電源をオフにするとすべての情報が消滅してしまいます。そのため,外部メモリから回路情報を書き戻す処理が必要となり,結果的に無駄な電力を消費してしまいます。これに対し,不揮発FPGAにおいては,情報を電気ではなくスピン (磁石の向き)で記憶するため電源無しでも回路情報を保持することができます。したがって復帰動作は不要で,何も処理していないときに電源をオフにすることで無駄な待機電力を完全にカットすることができます(図2)。

MTJ/MOSハイブリッド回路技術の効果

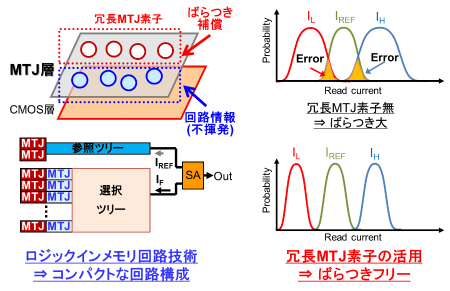

さらに,当研究室では単純な記憶機能の不揮発化だけではなく,MTJ素子が抵抗値で情報を記憶する素子であることに着目し,回路構造を工夫することで,FPGAの基本回路であるルックアップテーブル回路の大幅なコンパクト化を達成しています。また,MTJ素子がトランジスタ上に積層されるという特徴に着目し,素子を冗長に配置することで素子どうしの特性ばらつきを相殺できる手法を提案しています (図2) [文献1, 文献2]。

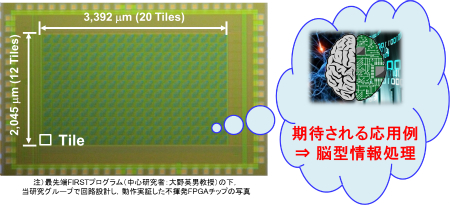

こういった考え方に基づき,当研究室では最先端プログラム (リーダー: 大野英男教授)のもと,NECとの共同研究で不揮発FPGAチップを実装,その動作を実証しております[文献3]。今後,この不揮発FPGAの低消費電力性や柔軟性を活用し,人間的判断が可能な情報処理などへの応用が期待されております。

参考文献:

- D. Suzuki, et al., "Fabrication of a nonvolatile lookup-table circuit chip using magneto/semiconductor-hybrid structure for an immediate-power-up field programmable gate array," VLSI Circuits Dig. Tech. Papers, pp80-81, 2009.

- D. Suzuki, et al., "Six-input lookup table circuit with 62% fewer transistors using nonvolatile logic-in-memory architecture with series/parallel-connected magnetic tunnel junctions," Journal of Applied Physics, vol.111, pp.07E318~1-07E318~3, 2012.

- D. Suzuki, et al., "Fabrication of a magnetic tunnel junction-based 240-tile nonvolatile field-programmable gate array chip skipping wasted write operations for greedy power-reduced logic applications," IEICE Electronics Express, vol. 10, no. 23, pp. 20130772~1-20130772~10, 2013.