高速双方向非同期データ転送

今や数GHzにも及ぶプロセッサのクロック周波数ですが、配線遅延によるクロックスキュー・ノイズ・消費電力の増大とクッロク信号自体が引き起こす問題が深刻になってきています。そこで、クロックを用いる同期式制御とは根本的に異なるクロックを使用しない非同期式制御によるVLSIシステムに関する研究を行っています。非同期式回路は局所的に逐次動作をするその特性から高速・低消費電力・高環境適応・低ノイズなど様々なメリットがあります。しかしながら、非同期式制御では要求応答に基づくハンドシェーク通信が必要なため、信号は常に往復することとなり、とりわけデータ転送においてはそのオーバヘッドが顕著となります。

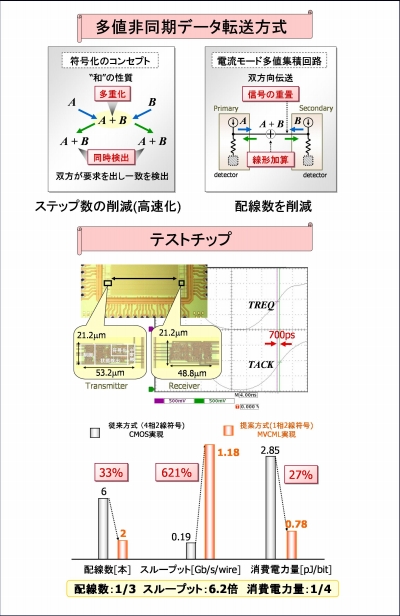

そこで本研究室では、多値符号化と多値回路技術の工夫によって高速な非同期データ転送を実現しています。下図のに示すように双方のモジュールからの信号を加算して、その結果を双方で受け取ると互いに相手の情報を同時に検出できるという“和”の性質に着眼し、双方のデータと制御信号を重畳させることにより要求応答処理を実質同時に行うことができます。さらに、回路技術に電流モード多値回路を用いることで、1線上に多レベルの信号を重畳かつ加算を結線のみでできることから、少ない配線で高速に非同期データ転送を実現します。また、この基盤技術を用いて大規模非同期VLSIシステムの開発も行っています。

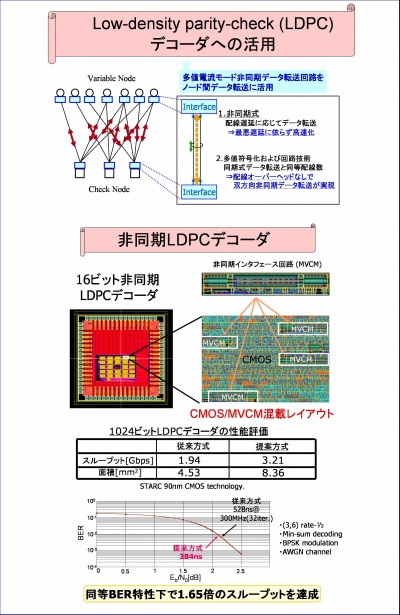

非同期LDPCデコーダ

低密度パリティチェック(Low-Density Parity-Check:LDPC)符号は誤り訂正符号の一種で、他の誤り訂正符号(ターボ符号、畳込み符号)と比較して高い誤り訂正能力を持つことから、次世代通信規格であるDVB-S2,10GBase-T,IEEE802.16e等への採用が決まっています。その一方でLDPC符号を復号するLDPCデコーダ、特に並列型では演算ノード間における配線数が膨大なものとなりチップ内配線が複雑になってしまいます。その結果演算ノード間におけるデータ転送遅延が低速となり、LDPCデコーダの高速化が困難でした。

そこで本研究室では、上記で提案してきた高速双方向非同期データ転送をLDPCデコーダのノード間データ転送に活用した「非同期LDPCデコーダ」について研究を行っています。非同期データ転送は要求・応答に基づくハンドシェイク通信に基づくため、同期式制御による最悪遅延に制約されず、実際の配線遅延でデータ転送が実現することから高速化が可能となります。また、高速双方向非同期データ転送の1ビットあたりの配線数は2本であり、これは同期式制御における1ビットあたりの配線数と同等であることから、配線数オーバーヘッドなしで高速なLDPCデコーダが実現します。