多値論理回路技術

今や1チップに十数億個のトランジスタが集積できるVLSI加工技術が発展してきましたが、消費電力が100Wを超え放熱の問題や、モバイル用のチップにおいては電池の持ちが悪くなるといった問題が生じています。また、これに伴って、配線量が膨大となり、配線による性能劣化という問題も起こってきています。現在のコンピュータは、0と1の2進数、つまり2値論理の世界で計算を行っています。つまり、チップ内の1本の配線に1ビットの情報を重畳し、1個のトランジスタで1ビット分の演算を実行させています。

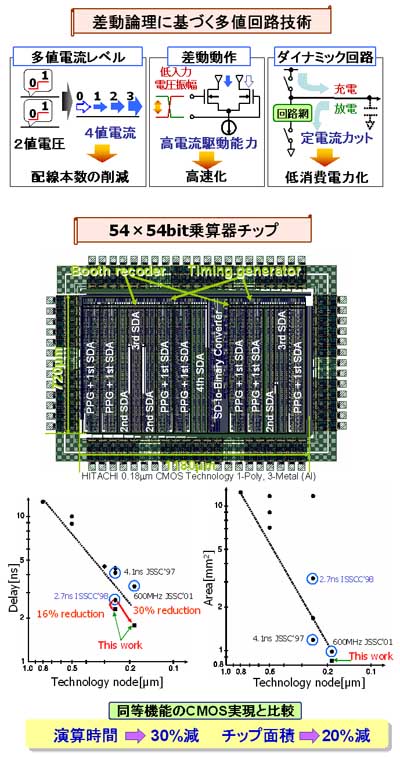

本研究室では、1つの配線に0、1、2、3といった多レベルの情報を重畳し、1つのトランジスタで多ビット情報を同時に処理させる「多値論理回路」技術について研究を行っています。1つの配線に多ビット情報を重畳することにより、配線数を削減でき、また配線の複雑さを解消することが可能です。さらに、値を電流で表現することで、加減乗除などの算術演算の基本となる足し算を、配線をつなぐだけで行えるといったメリットがあり、高速かつコンパクトにVLSIを実現可能な技術です。他にも、チップが消費する総電流量を制限できるために、現在、数GHzといった高周波数で動作させる場合も電力消費を削減が可能です。また、高速なスイッチが可能な差動対回路を活用することで処理の高速化を図り、ダイナミック論理といったさらに電流量を削減できる手法により、電力の削減が可能となります。以上のような多くの利点を持つ「多値論理回路」技術により、VLSIのさらなる高性能化を目指して研究を行っています。