不揮発性ロジック

電源を切ってもデータを記憶し続ける不揮発性材料・デバイスは、通常、コンピュータの起動プログラムなどを内蔵するROM(Read-Only Memory)として使用されています。ROMの最大の特長は、データを保持している間、電力を消費しない点です。この特長に着目して、ROMなどの不揮発性メモリとしてだけでなく、CPUなど演算器やシステム全体の構成にも、この「不揮発性」を積極的に活用する回路・システム構築方法が「不揮発性ロジック」です。本研究室では、「不揮発性ロジック」研究の重要性を世界で初めて提唱し、その研究に取り組んでいます。今までの回路・システム構成方法と比較し、不揮発性ロジックに基づく方法は以下のような特徴ある回路・システム構成に適しております。

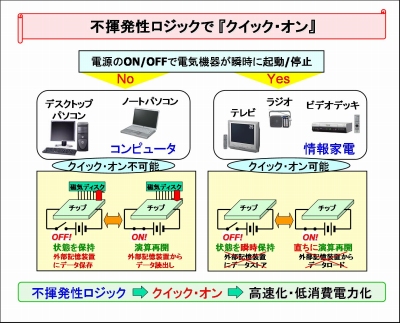

◆クイックオン機能を有するシステム構成

不揮発性ロジックでは、記憶機能を演算回路に分散して記憶できます。また不揮発性記憶なので、電源を切っても記憶データを保持できます。この機能に着目すれば、①もし電源をオフしてもチップ外ハードディスクにデータを退避不要で、②電源を再度オンすれば、ハードディスクから記憶データを呼び出す必要なく瞬時に演算を開始できる、こととなります。これを「クイックオン」機能と呼びます。現有のモバイル機器では、スイッチをOFFしても実際には電源がカットオフされておらず、まず現在の内部状態がハードディスクなどの外部記憶メディアに退避させる操作が行われます。その退避時間、退避に要する電力などが今後システムが複雑化・高機能化するに連れて益々増大する傾向にあります。このようなシステム上の本質的問題点を解決する一手法が、不揮発性ロジックです。

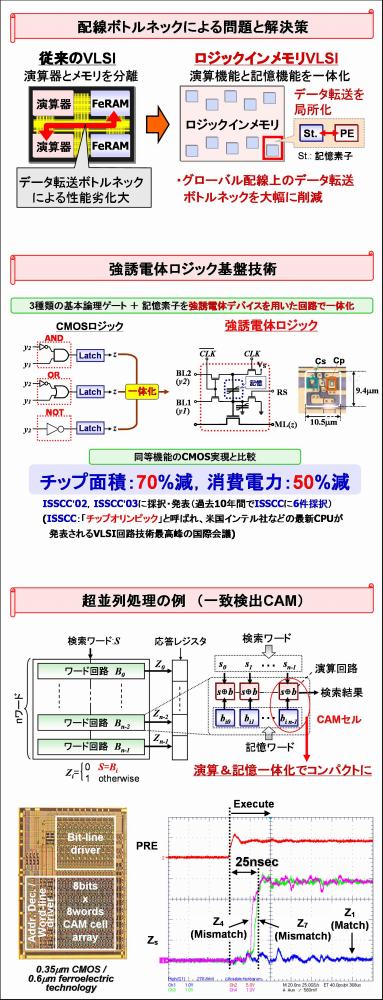

◆超並列処理構造を有するシステム構成

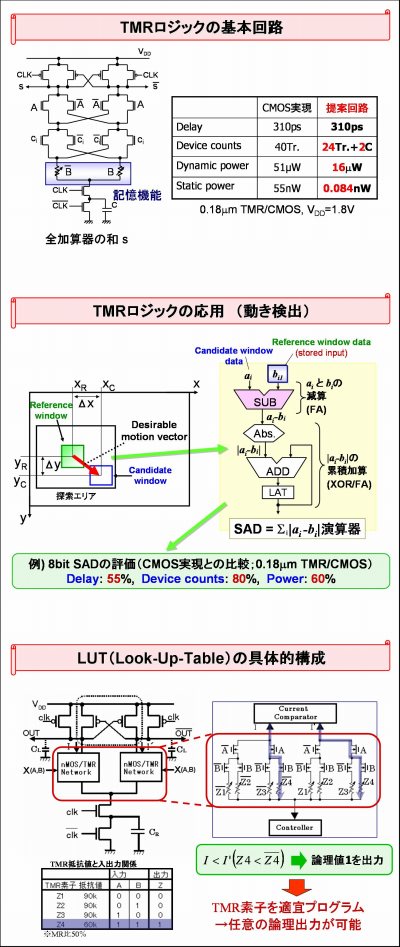

現在のプロセッサ・チップでは、トランジスタなどの能動素子自体よりもむしろ、配線など受動素子に起因して、システム全体の性能劣化を引き起こしています。例えば、現在の集積回路技術で超並列処理を実行させる場合、メモリと演算器間の配線を駆動してデータ転送する部分がボトルネックとなっています。このメモリ・演算器間データ転送ボトルネックを本質的に解決し、超並列処理を実現する1つの解決方法として、本研究では、記憶機能と演算機能を回路レベルでコンパクトに一体化する回路技術を研究しています。不揮発性デバイス本来の記憶機能を活用しつつ、演算機能も同時に実現する回路技術を考案することで、記憶機能と演算機能をコンパクトに一体化できるわけです。本研究グループでは、強誘電体キャパシタを活用して、記憶・演算機能を回路レベルで一体化する基本回路技術を実チップ試作を通じて既に原理動作を実証済みです。この回路技術に基づき、より大規模な応用例での性能評価や、強誘電体キャパシタ以外の不揮発性デバイス、例えばMRAMセル回路の構成要素、TMR(Tunneling-Magneto-Resistive)素子などを活用した不揮発性演算回路技術についても総合的に検討し、不揮発性デバイス活用による全く新しいコンピューティングパラダイムの構築を目指しております。このような点から、不揮発性ロジック回路として、超並列処理に適するシステム応用例として、連想メモリ(CAM)などについて具体的にシステム構成し、性能を定量的に評価しています。

◆動的再構成可能機能を有するシステム構成

ハードウェア構造はそのままで、その機能がさまざま変化するハードウェアが再構成可能回路・システムです。例えば、FPGA(Field-Programmable Gate Array)はその典型例です。FPGAのようなプログラム機能を有しながら、専用チップのような高い性能が実現できれば、応用分野がさらに拡大することが期待できます。つまり、さまざまな演算機能をハードウェア固定のまま自由にプログラムでき、しかも高速処理可能で、電力消費も大幅に削減できるという夢のような次世代のハードウェア技術に基づいてプロセッサを構成すれば、同じ1つのプロセッサを使いながらも、携帯電話から音楽プレーヤーに瞬時に「変身」する、まるでカメレオンのような次世代集積回路チップが実現できることとなります。不揮発性ロジックでは、演算機能として多種類の論理演算機能を実現できます。この多機能性を活用し、瞬時に演算機能を切り替えられる動的再構成VLSIの実現が可能となります。現状の動的再構成VLSIでは、演算機能を切替え、かつその状態を保持するための制御回路と記憶回路を別途追加する必要があり、複雑な構成となってしまいます。そこで、不揮発性ロジック回路技術を活用することで、さまざまな機能を全て一体化した形態でコンパクトに実現する方法を研究しています。

[期待される成果]

本研究で開発する不揮発性ロジックインメモリVLSIでは、ハードウェア構成を変更せずに、任意の演算回路や記憶機能を内蔵した順序回路を実現できます。この機能は製造マスクを全て共通に利用(リユース)できるFPGAと同じ特長です。半導体チップの単価はこのマスク代の比重が極めて高く、もしこれを全てのチップで共通に利用できれば、半導体チップの製造コストを激減できることとなります。しかしながら、現状のFPGAではプログラマブルな機能の付加に伴い、ASICのような専用VLSI実現と比較し、性能が著しく低くなるという問題がありました。本研究グループで考案した提案の不揮発性ロジックでは、大局的配線問題の解決と記憶・演算機能の融合による多機能回路モジュールを極めてコンパクトに実現できるため、上述した「製造マスクのリユース」と「ASIC並みの高性能化」を同時に達成できます。すなわち、高性能でありながら極めて安価にチップ開発ができるということとなり、現状の半導体チップの設計方法・製造プロセスを全てこの方法に切り替える「チップ革命」を与えることが可能となります。この技術を世界に先駆けて日本から発信できれば、再度「半導体立国・日本」のルネッサンスが訪れるものと確信しています。