|

|

|

High-speed duplex asynchronous data transfer

With recent rapid feature size scaling, the factor that determines the circuit performance is increasingly shifted from devices to interconnect. Global interconnect not only limits the clock frequency, but causes clock-skew problems in synchronous system. For this reason, an alternative approach which has different sense of direction from the existing approach is expected. Asynchronous design, where timing is managed locally, is one of the possible approaches to solve the above serious interconnection problem because the asynchronous design has many features which are low power dissipation, high speed and robustness. However, communication-steps overhead caused by the handshaking much affects the cycle time.

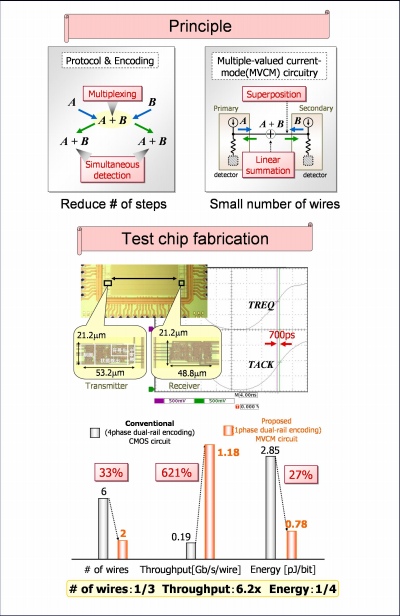

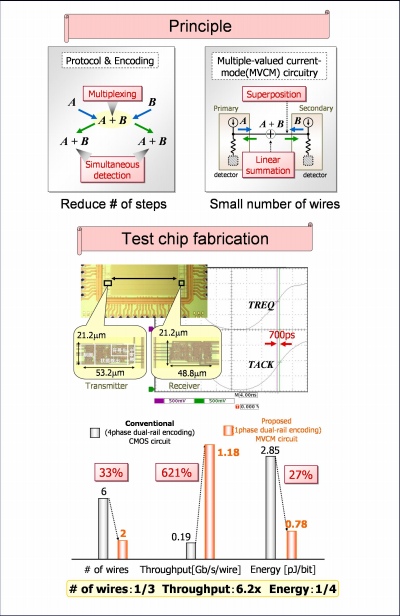

In our laboratory, high-speed asynchronous data-transfer scheme has been proposed based on multiple-valued encoding and multiple-valued current-mode (MVCM) circuits. Since mutual states are detected by observing the sum of information at both modules, the number of communication steps can be reduced as shown in below figure. Moreover, the mutual information can be multiplexed on dual-rail wires by using the MVCM circuits because the linear summation is realized by just wiring, which results in reduction of the number of wires.

Asynchronous LDPC decoder

Due to their capacity-approaching performance, Low-Density Parity-Check (LDPC) codes have been proposed for numerous recent data communications standards such as DVB-S2, IEEE 802.16e, and 10GBASE-T. Decoding algorithm can be easily performed in parallel by every vertex; fully parallel hardware implementations tend to be routing dominated, which limits throughput by available die area and the ability for computational kernels to transmit data to each other over the interleaver between computation nodes.

One approach to solving the problem is to utilize the high-speed duplex asynchronous data transfer which is introduced above in the LDPC decoder. The use of the asynchronous system makes it possible to realize a high-speed data transfer which is not restricted by the worst-case delay. Moreover, since the proposed asynchronous data transfer is performed by just two-wire which is the same number of wires in the synchronous system, high-throughput LDPC decoder is realized without wiring overhead.

|

|